Autoren:

Sascha Lohse (Finetech GmbH & Co. KG)

Alexander Wollanke (Fraunhofer IZM-ASSID)

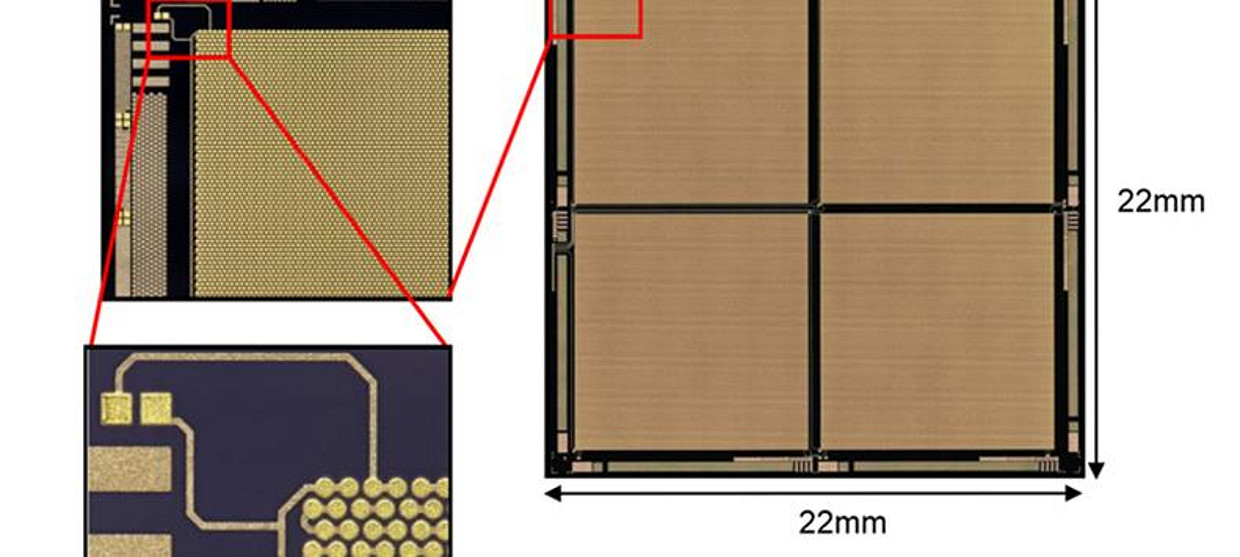

Zusammenfassung: Im Zusammenhang mit dem Wunsch nach kleineren, leichteren und stetig mehr Funktionen in sich vereinenden elektronischen Geräten werden an IC-Packages immer härtere Anforderungen gestellt. Zunehmend komplexere Schaltungen, kleine Pitches, Micro-Bump Designs sowie die Nutzung von Die Stacking sind typische Beispiele, wie die Industrie auf diese Entwicklung zu reagieren versucht. Eine geeignete Prozesstechnologie für das 3D Packaging zu finden ist eine Herausforderung. Dieses Whitepaper stellt Informationen zu verschiedenen Verbindungsmethoden bereit, die heutzutage im 3D Packaging vorwiegend zum Einsatz kommen. In umfassenden Versuchen wurden verschiedene Dies, alle gekennzeichnet durch eine hohe Bumpzahl (bis 143.000), kleinen Pitch (bis 25 µm) und kleinen Bump-Durchmesser (bis 13 µm), mit Hilfe eines FINEPLACER® sigma auf ein Substrat gebondet. Das Paper beschreibt die Testverfahren für unterschiedliche 3D-Integrationstechnologien und verweist auf angewendete Prozessparameter sowie die erzielten Ergebnisse.

[Sprache des Whitepapers: Englisch]