Autoren:

Lyubomir Kerachev, Yves Lembeye, Jean-Christophe Crébier (Grenoble Electrical Engineering Laboratory)

Christoph Daedlow (Finetech GmBH & Co. KG)

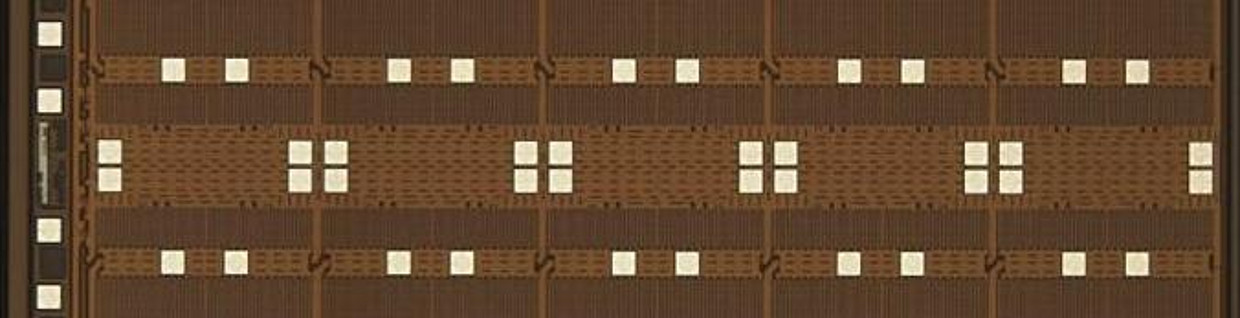

Zusammenfassung: Standard-IC-Schaltungen mit einer erhöhten Anzahl an I/O Pads sind bei normierten Montageanforderungen größer, teurer und weisen erhöhte Widerstände beim Wirebonden sowie parasitäre Induktivitäten auf. Mit Hilfe des Flip Chip Bondens kann das Chip-Package deutlich kompakter gehalten werden, was die Montagekosten senkt und unerwünschte parasitäre Phänomene wie Widerstand und Induktivität der Pads verringert. Zusätzlich kann die Anzahl der Wärmeschnittstellen zwischen Chip und Substrat, die als hauptsächlicher Pfad für die Wärmeabfuhr dienen, kleiner gehalten werden. Das Paper stellt Tests zur Einschätzung kommerziell verfügbarer Mikromontagen wie anisotropische Klebetechnologien, Thermokompressionsbonden, Thermosonisches / Ultraschallbonden und Löten vor. Auch speziell entwickelte Flip-Chip-Techniken, die am Solder Bumping angelehnt sind, werden vorgeschlagen und experimentell beschrieben. Ziel dieser Arbeit ist es, die geeigneteste Flip-Chip-Bondtechnologie für CMOS Schaltkreise mit erhöhter Padzahl und komplexer Oberflächenstrukturierung zu ermitteln.

[Sprache des Whitepapers: Englisch]